Предмет: Операционные системы.

Вопрос: №5

***

—————————————————————

Фон Неймавская архитектура вычисли-тельных машин:

Любой IBM PC-совместимый компьютер представляет собой реализацию фон-неймановской архитектуры вычислительных машин. Машина состоит из:

1.) блока управления;

2.) арифметико-логического устройства

(процессор);

3.) памяти;

4.) устройств ввода-вывода.

В ней реализуются следующие принципы организации архитектуры:

– концепция хранимой программы (программы и данные хранятся в одной и той же памяти);

– последовательная передача управления. (выполняемые действия определяются блоком управления и АЛУ, которые вместе являются основой центрального процессора. Центральный процессор выбирает и исполняет команды из памяти последовательно, адрес очередной команды задается «счетчиком адреса» в блоке управления).

Подавляющее большинство современных компьютеров основаны именно на указанных принципах, включая и сложные многопроцессорные комплексы, которые можно рассматривать как объединение фон-неймановских машин.

Процессор имеет набор регистров, часть которых доступна для хранения операндов, выполнения действий над ними и формирования адреса инструкций и операндов в памяти. Другая часть регистров используется процессором для служебных (системных) целей, доступ к ним может быть ограничен (есть даже программно-невидимые регистры). Все компоненты компьютера представляются для процессора в виде наборов ячеек памяти или/и портов ввода-вывода, в которые процессор может производить запись и/или считывать содержимое.

—————————————————————

Ячейки памяти, порты, регистры:

Ячейки памяти служат лишь для хранения информации. Сначала информацию записывают в ячейку, а потом могут прочитать, а также записать иную информацию.

Порты ввода-вывода, как правило, служат для преобразования двоичной информации в какие-либо физические сигналы и обратно. (например, порт данных параллельного интерфейса формирует электрические сигналы на разъеме, к которому обычно подключают принтер. Порт состояния того же интерфейса электрические сигналы, поступающие от принтера, отображает в виде набора бит, который может быть считан процессором.)

Регистр – довольно широкое понятие, которое зачастую используется как синоним порта.

Каждый байт (ячейка памяти, порт) имеет собственный уникальный физический адрес, устанавливаемый на системной шине процессором при инициировании обращения к данной ячейке или порту.

В семействе х86 и PC-совместимых компью-терах пространства адресов ячееек памяти и портов ввода/вывода разделены. Нынешние процессоры имеют разрядность физического адреса памяти 32 и даже 36 бит, что позволяет адресовать до 4 и 64 Гбайт соответственно. Пространство ввода/вывода использует только младшие 16 бит адреса, что позволяет адресовать до 65384 однобайтных регистров. Пространства памяти и портов ввода/вывода неравнозначны не только по объему, но и по способам обращения. Способов адресации к ячейке памяти в х86 великое множество, в то время как для адресации ввода/вывода их только два.

К памяти возможна (и широко используется) виртуальная адресация, при которой для программиста, программы и даже пользователя создается иллюзия гигантского размера оперативной памяти.

К портам ввода-вывода обращаются только по реальным адресам, правда, и здесь возможна виртуализация, но уже чисто программными средствами операционной системы.

Самое существенное различие пространств памяти и портов ввода-вывода: процессор может считывать инструкции для исполне-ния только из пространства памяти; через порт ввода можно считать фрагмент программного кода, что и происходит, например, при считывании данных с диска, но для того, чтобы этот код исполнить, его необходимо записать в память.

—————————————————————

Адресация ячеек памяти в реальном режиме:

От процессоров 8086/88 достался своеобразный образ задания адреса ячейки памяти в виде указателя «seg:offset».

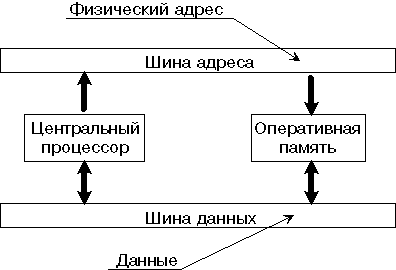

Для работы с памятью используются две шины – шина адреса и шина данных. Физически память устроена таким образом, что возможна адресация как 16-битовых слов, так и отдельных байтов памяти. Кроме того, процессоры i80386 и i80486 могут адресовать 32-битовые слова памяти.

В любом случае так называемый физический адрес передаётся из процессора в память по шине адреса. Ширина шины адреса определяет максимальный объём физической памяти, непосредственно адресуемой процессором.

Например, компьютер IBM XT оснащён 20-разрядной шиной адреса и 16-разрядной шиной данных. Это означает, что имеется возможность адресоваться к 216 байтам памяти, т.е. к 1 мегабайту памяти. Причём возможно адресоваться к байтам и словам размером в 16 бит.

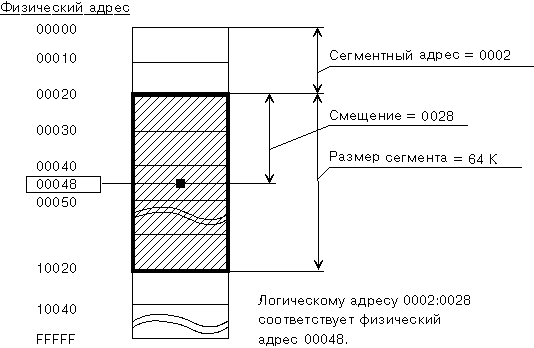

Так как адреса принято записывать в шестнадцатеричной форме, то можно записать диапазон физических адресов для 20-разрядной шины адреса следующим образом:

00000h<=[физический адрес]<=FFFFFh

Таким образом, для представления физического адреса в компьютерах IBM PC и IBM XT используется двадцать двоичных или пять шестнадцатеричных разрядов.

Однако все регистры процессора i8086 являются 16-разрядными. Возникает проблема представления 20-разрядного физического адреса памяти при помощи содержимого 16-разрядных регистров.

Для разрешения этой проблемы используется двухкомпонентный логический адрес.

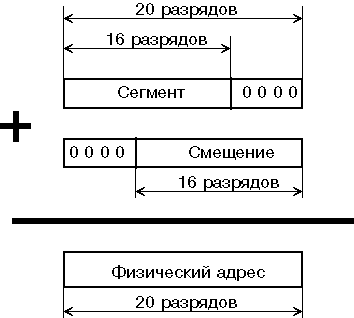

Логический адрес состоит из 16-разрядных компонент: компоненты сегмента памяти и компоненты смещения внутри сегмента.

Для получения 20-разрядного физического адреса к сегментной компоненте приписывается справа четыре нулевых бита (для расширения до 20 разрядов), затем полученное число складывается с компонентой смещения. Перед сложением к компоненте смещения слева дописывается четыре нулевых бита (также для расширения до 20 разрядов).

При запуске программы ей выдается несколько сегментов. Каждый сегмент должен иметь свой адрес, кратный 16 и размер не более 64 кбайт. Чтобы получить доступ к данным внутри сегмента используется смещение. Смещение – адрес, отсчитываемый от начала сегмента. Так как сегмент занимает не более 64 кбайт, то для хранения смещения хватит 16 разрядов.

Address = 16*seg+offset.

Вообще оперативная память занимает не все пространство, а только младшие 640 кбайт. Её можно разделить на 10 сегментов максимального размера (64 кбайт). Обычно далеко не все сегменты имеют максимальный размер, поэтому их количество бывает больше 10. И вообще, пространство от 64 кбайт до 1 Мбайт выделено для размещения BIOS, её дополнений, расположенных на платах контроллеров внешних устройств, адресов, через которые происходит доступ к этим устройствам, и т.п.

—————————————————————

Организация и адресация памяти в защищенном режиме:

В защищенном режиме, также как и в реальном, существуют понятия логического и физического адреса. Кроме сегментации в защищенном режиме возможно разбиение (Paging) логической памяти на страницы размером 4 Кбайт, каждая из которых может отображаться на любую область физической памяти. Начиная с 5-го поколения, появилась возможность увеличения размера страницы до 4 Мбайт. Сегментация и разбиение на страницы могут применяться в любых сочетаниях. Сегментация является средством организации логической памяти на прикладном уровне. Разбиение на страницы

применяется на системном уровне для управления физической памятью. Сегменты и страницы могут выгружаться из физичес-кой оперативной памяти на диск и по мере необходимости подкачиваться с него обратно в физическую память. Таким образом реализуется виртуальная память.

Применительно к памяти различают три адресных пространства: логическое, линейное и физическое.

Основным режимом работы 32-разрядных процессоров считается защищенный режим,

в котором работают все механизмы преобразования адресных пространств.

Логический адрес (или виртуальных адрес) состоит из селектора сегмента и эффективного адреса (смещения), обозначается seg:offset.

Преобразование логического адреса в физический выполняется не простым сложением со сдвигом, а при помощи специальных таблиц преобразования адресов (специальной области памяти). В первом приближении можно считать, что селектор для процессора i80286 является индексом в таблице, содержащей базовые 32 разрядные адреса сегментов (и не только). В процессе преобразования логического адреса в линейный процессор прибавляет к базовому 32-разрядному адресу 32-разрядное смещение, т.е. линейный адрес образуется сложением базового адреса сегмента с эффективным адресом.

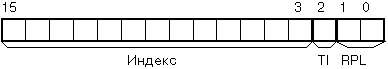

Из чего состоит селектор: не все 16 бит селектора используются для индексации по таблице адресов. В качестве индекса выступают старшие 13 бит. Два младших бита (бит 0 и бит 1) используются системой защиты памяти. Бит 2 позволяет выбирать для преобразования адреса один из двух типов преобразования адресов.

Поле TI (Table Indicator) состоит из одного бита. Если этот бит равен нулю, для преобразования адреса используется так называемая глобальная таблица дескрипторов GDT (Global Descriptor Table), в противном случае – локальная таблица дескрипторов LDT (Local Descriptor Table).

Таблица дескрипторов – это просто таблица преобразования адресов, содержащая базовые адреса сегментов и некоторую другую информацию. То есть каждый элемент таблицы дескрипторов (дескриптор) содержит базовый адрес сегмента и другую информацию, описывающую сегмент.

Таблица GDT – единственная в системе. Обычно в ней находятся описания сегментов операционной системы. Таблиц LDT может быть много. Эти таблицы содержат описания сегментов программ, работающих под управлением операционной системы, т.е. отдельных задач. В каждый данный момент времени процессор может использовать только одну таблицу LDT.

Эффективный адрес формируется сложением компонентов base, index, displacement с учетом масштаба scale.

32-битный физический адрес памяти об-разуется после преобразования линейного адреса блоком станичной переадресации. В простейшем случае при отключенном блоке страничной переадресации физический адрес совпадает с линейным. Включенный блок станичной переадресации осуществляет трансляцию линейного адреса в физический страницами размеров 4 Кбайт (для последних поколений процессоров возможны станицы размером 2-4 Mбайт). Блок обеспечивает и расширение разрядности физического адреса процессоров шестого поколения до 36 бит. Блок переадресации может включаться только в защищенном режиме.

Для обращения к памяти процессор совместно с внешними схемами формирует внешние сигналы для операций записи и чтения. Шина адреса разрядностью 32-36 бит позволяет адресовать 4/64 Гбайт физической памяти, но в реальном режиме доступен только 1 Мбайт, начинающийся с младших адресов.